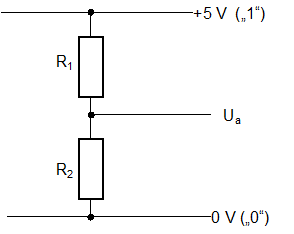

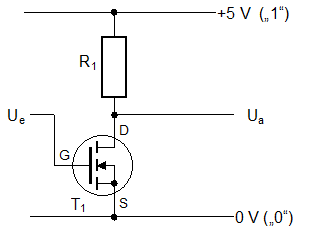

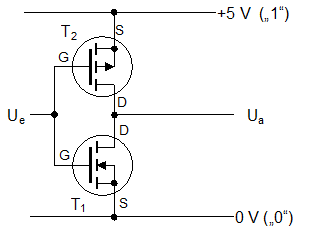

| Ue | Ua |

|---|---|

| 0 Volt | ≈5 Volt |

| 5 Volt | ≈0 Volt |

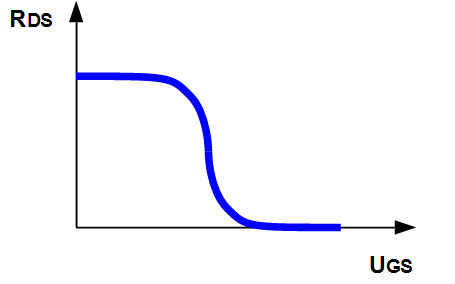

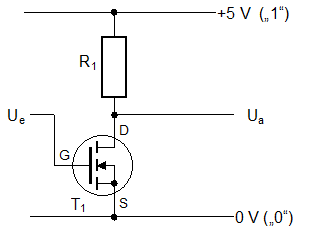

| E | A |

|---|---|

| "0" | "1" |

| "1" | "0" |

| E | T1 | T2 | A |

|---|---|---|---|

| "0" | sperrt | leitet | "1" |

| "1" | leitet | sperrt | "0" |

|

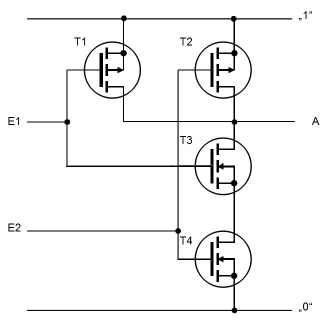

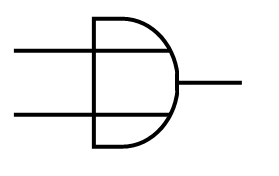

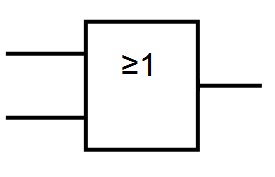

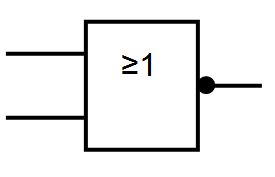

A = E1 OR E2

Das Ausgangssignal A ist also genau dann gleich 1, wenn mindestens einer der Eingänge E1 oder E2 gleich 1 ist. |

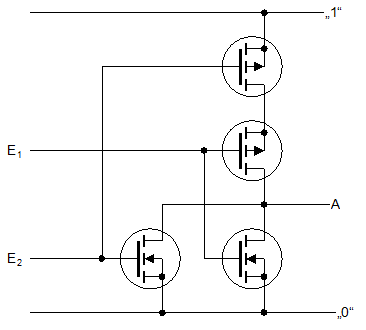

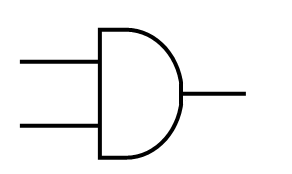

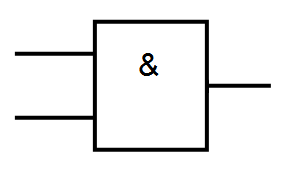

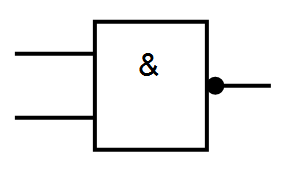

A = E1 AND E2

Das Ausgangssignal A ist also genau dann gleich 1, wenn sowohl E1 als auch E2 gleich 1 sind. |

| E1 | E2 | T1 | T3 | T2 | T4 | A |

|---|---|---|---|---|---|---|

| 0 | 0 | leitet | sperrt | leitet | sperrt | 1 |

| 1 | 0 | sperrt | leitet | leitet | sperrt | 1 |

| 0 | 1 | leitet | sperrt | sperrt | leitet | 1 |

| 1 | 1 | sperrt | leitet | sperrt | leitet | 0 |

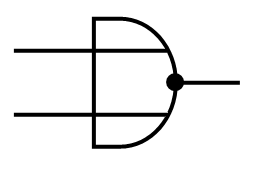

| E1 | E2 | A |

|---|---|---|

| 0 | 0 | 1 |

| 1 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 1 | 0 |

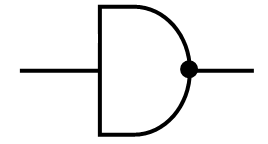

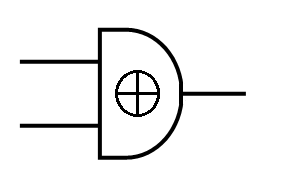

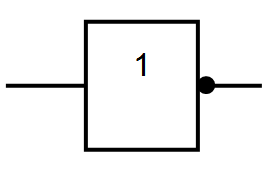

| NOT | AND | OR | NAND | NOR | XOR | |

|---|---|---|---|---|---|---|

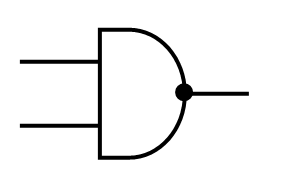

| DIN 40700 (1963) |

|

|

|

|

|

|

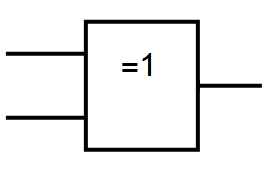

| IEC 60617-12 (1997) |

|

|

|

|

|

|

aus E1 NAND E2 = NOT (E1 AND E2) folgt:Versuchen Sie mal, die beiden vorstehenden Zeilen genau zu verstehen; wenn Sie das geschafft haben, dann müssen Sie auch selbst auf die obengenannte "gute Idee" kommen!

NOT (E1 NAND E2) = NOT (NOT (E1 AND E2)) = E1 AND E2

|

|